These tools support and simplify the development of today’s advanced programmable systems, which include CPU cores, digital signal processing (DSP) blocks and multiple IP sub-systems. The high-level design tools Altera offers include system-level C-based, IP-based and model-based design entry systems. These enhancements further enable customers’ to rapidly design, implement and get to market using Altera® devices.Īccelerating System Development with High-level Design Tools

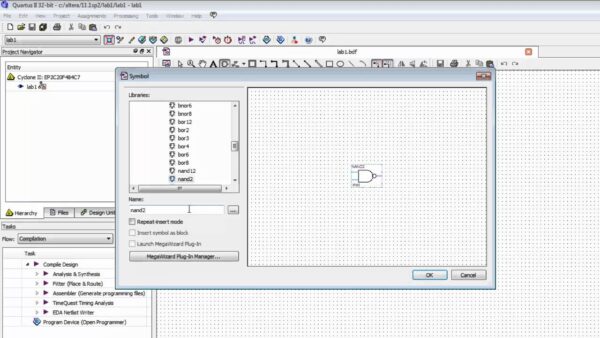

#ALTERA QUARTUS II V12.1 WEB EDITION SOFTWARE#

Also included in the latest software release are several enhancements, such as a partial reconfiguration design flow, new intellectual property (IP) cores and expanded support for 28 nm FPGAs and SoC FPGAs.

Quartus II software version 12.1 bolsters its support for high-level design flows with the inclusion of an SDK for OpenCL™, and enhancements to both its Qsys system integration tool and DSP Builder model based design environment. The latest version strengthens the Quartus II software’s high-level design environment by continuing to ease traditional hardware development tasks so users can maximize productivity while benefiting from the broad range of leading-edge capabilities of Altera devices. San Jose, Calif., November 19, 2012– Altera Corporation (Nasdaq: ALTR) today announced the release of its Quartus® II software version 12.1, the industry’s number one design suite in performance and productivity for CPLD, FPGA, SoC FPGA and HardCopy® ASIC designs. Altera Quartus II Software Version 12.1 Accelerates System Development with Enhanced High-Level Design FlowsĪddition of Altera’s SDK for OpenCL to Altera’s High-level Design Flows Improves Designer Productivity and Increases System Performance

0 kommentar(er)

0 kommentar(er)